SpinalHDL

Nach dem Vortrag über SpinalHDL auf dem 33C3 habe ich die IceStorm Tool-Chain unter MacOS damit endlich mal ausprobiert:

Anleitung für die Installation: McMayer.

Integration in SBT war dann einfach:

import scala.sys.process._

name := "blinky"

scalaVersion := "2.11.6"

libraryDependencies ++= Seq(

"com.github.spinalhdl" % "spinalhdl-core_2.11" % "latest.release",

"com.github.spinalhdl" % "spinalhdl-lib_2.11" % "latest.release"

)

lazy val synth = taskKey[Unit]("Synthesize bitstream")

lazy val prog = taskKey[Unit]("Program ICE40")

synth := {

val yoSys = Seq("yosys", "-p", "synth_ice40 -top Blink -blif target/Blink.blif", "Blink.v")

val arachne = Seq("arachne-pnr", "-d", "8k", "-P", "ct256", "-o", "target/Blink.asc", "-p", "Blink.pcf", "target/Blink.blif")

val icepack = Seq("icepack", "target/Blink.asc", "target/Blink.bin")

(runMain in Compile).toTask(" de.ideasinlogic.fpga.spinal.blink.Blink").value

yoSys #&& arachne #&& icepack !

}

prog := {

val iceprog = Seq("iceprog","-S","target/Blink.bin")

iceprog !

}

IO-Definition des ICE40-HX8K Demo-Boards:

set_io io_clk J3

set_io io_led[7] C3

set_io io_led[6] B3

set_io io_led[5] C4

set_io io_led[4] C5

set_io io_led[3] A1

set_io io_led[2] A2

set_io io_led[1] B4

set_io io_led[0] B5

SpinalHDL Code:

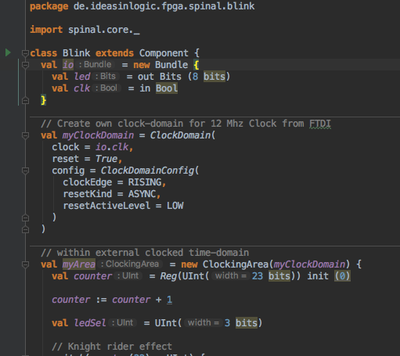

package de.ideasinlogic.fpga.spinal.blink

import spinal.core._

class Blink extends Component {

val io = new Bundle {

val led = out Bits (8 bits)

val clk = in Bool

}

// Create own clock-domain for the

// 12 Mhz Clock from the FTDI chip

val myClockDomain = ClockDomain(

clock = io.clk,

reset = True,

config = ClockDomainConfig(

clockEdge = RISING,

resetKind = ASYNC,

resetActiveLevel = LOW

)

)

val myArea = new ClockingArea(myClockDomain) {

val reg = Reg(UInt(23 bits)) init (0)

reg := reg + 1

val ledSel = UInt(3 bits)

switch(reg(22).asUInt) {

is(1) {

ledSel := 7 - reg(21 downto 19)

}

default {

ledSel := reg(21 downto 19)

}

}

io.led := B"1" << ledSel

}

}

object Blink {

// Let's go

def main(args: Array[String]) {

SpinalVerilog(new Blink)

}

}